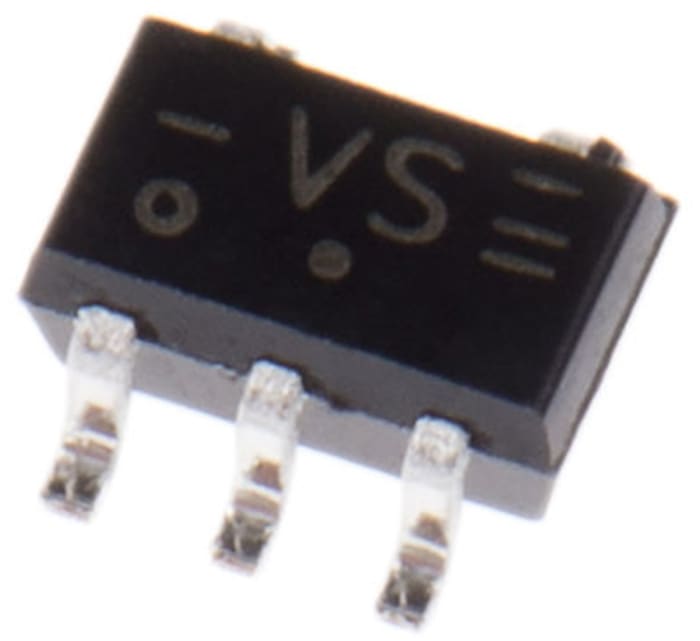

Y: Puerta lógica, SN74LVC1G08DCKR, LVC, CMOS 32mA SC-70 5 pines 2

Documentos Técnicos

Especificaciones

Brand

Texas InstrumentsFunción Lógica

Y

Tipo de montaje

Surface Mount

Número de Elementos

1

Number of Inputs per Gate

2

Tipo de Encapsulado

SC-70, SOT

Conteo de Pines

5

Familia Lógica

LVC

Tensión de Alimentación Máxima de Funcionamiento

5.5 V

Corriente Máxima de Salida de Alto Nivel

-32mA

Maximum Propagation Delay Time @ Maximum CL

5 ns @ 5 V

Tensión de Alimentación de Funcionamiento Mínima

1.65 V

Corriente Máxima de Salida de Bajo Nivel

32mA

Altura

1mm

Profundidad

1.4mm

Temperatura Mínima de Funcionamiento

–40 °C

Dimensiones

2.15 x 1.4 x 1mm

Temperatura Máxima de Funcionamiento

125 °C

Tipo de Salida

CMOS

Propagation Delay Test Condition

50pF

Largo

2.15mm

Datos del producto

Puertas lógicas de la familia 74LVC, Texas Instruments

Gama de Texas Instruments de puertas lógicas estándar de la familia 74LVC de los CI de lógica CMOS de baja tensión. La familia 74LVC utiliza tecnología CMOS de puerta de silicio y está diseñada para funcionar a 3,3 V, lo que permite una reducción significativa del consumo de energía en comparación con los sistemas de 5 V.

Intervalo de tensión de funcionamiento: 1,65 a 3,6 V

Entradas tolerantes de 5 V

Compatibilidad: entrada LVTTL/TTL, salida LVCMOS

El rendimiento de cierre excede 250 mA conforme a JESD 17

La protección contra ESD excede JESD 22

74LVC Family

$ 264.000

$ 88 Each (On a Reel of 3000) (Sin IVA)

$ 314.160

$ 104,72 Each (On a Reel of 3000) (IVA Inc.)

3000

$ 264.000

$ 88 Each (On a Reel of 3000) (Sin IVA)

$ 314.160

$ 104,72 Each (On a Reel of 3000) (IVA Inc.)

Volver a intentar más tarde

3000

Volver a intentar más tarde

| Cantidad | Precio Unitario sin IVA | Por Rollo |

|---|---|---|

| 3000 - 3000 | $ 88 | $ 264.000 |

| 6000 - 12000 | $ 71 | $ 213.000 |

| 15000+ | $ 66 | $ 198.000 |

Documentos Técnicos

Especificaciones

Brand

Texas InstrumentsFunción Lógica

Y

Tipo de montaje

Surface Mount

Número de Elementos

1

Number of Inputs per Gate

2

Tipo de Encapsulado

SC-70, SOT

Conteo de Pines

5

Familia Lógica

LVC

Tensión de Alimentación Máxima de Funcionamiento

5.5 V

Corriente Máxima de Salida de Alto Nivel

-32mA

Maximum Propagation Delay Time @ Maximum CL

5 ns @ 5 V

Tensión de Alimentación de Funcionamiento Mínima

1.65 V

Corriente Máxima de Salida de Bajo Nivel

32mA

Altura

1mm

Profundidad

1.4mm

Temperatura Mínima de Funcionamiento

–40 °C

Dimensiones

2.15 x 1.4 x 1mm

Temperatura Máxima de Funcionamiento

125 °C

Tipo de Salida

CMOS

Propagation Delay Test Condition

50pF

Largo

2.15mm

Datos del producto

Puertas lógicas de la familia 74LVC, Texas Instruments

Gama de Texas Instruments de puertas lógicas estándar de la familia 74LVC de los CI de lógica CMOS de baja tensión. La familia 74LVC utiliza tecnología CMOS de puerta de silicio y está diseñada para funcionar a 3,3 V, lo que permite una reducción significativa del consumo de energía en comparación con los sistemas de 5 V.

Intervalo de tensión de funcionamiento: 1,65 a 3,6 V

Entradas tolerantes de 5 V

Compatibilidad: entrada LVTTL/TTL, salida LVCMOS

El rendimiento de cierre excede 250 mA conforme a JESD 17

La protección contra ESD excede JESD 22